ISSCC2023 6.3 A 0.43pJ/b 200Gb/s 5-Tap Delay-Line-Based Receiver FFE with Low-Frequency Equalization in 28nm CMOS(6.3-5-tap低频均衡接收器FFE)

Bingyi Ye, Guangdong Wu, Weixin Gai, Kai Sheng, Yandong He

Peking University, Beijing, China

原文地址:https://ieeexplore.ieee.org/abstract/document/10067348

1. Background

对更大I/O带宽不断增长的需求已将收发器数据速率推至200 Gb/s [1]。在此速率下,判决反馈均衡器(Ddecision-feedback equalizers, DFE)的实施面临严重的时序约束。接收器(RX)中的离散时间前馈均衡器(Discrete-time feed-forward equalizers, FFE)中断定时环路并补偿电和光损伤[2-3]。然而,它依赖于精确、多相和高速采样时钟。本文提出了一种基于5抽头延迟线的FFE接收机,工作速率为200 Gb/s,均衡了17. 2dB的信道损耗。

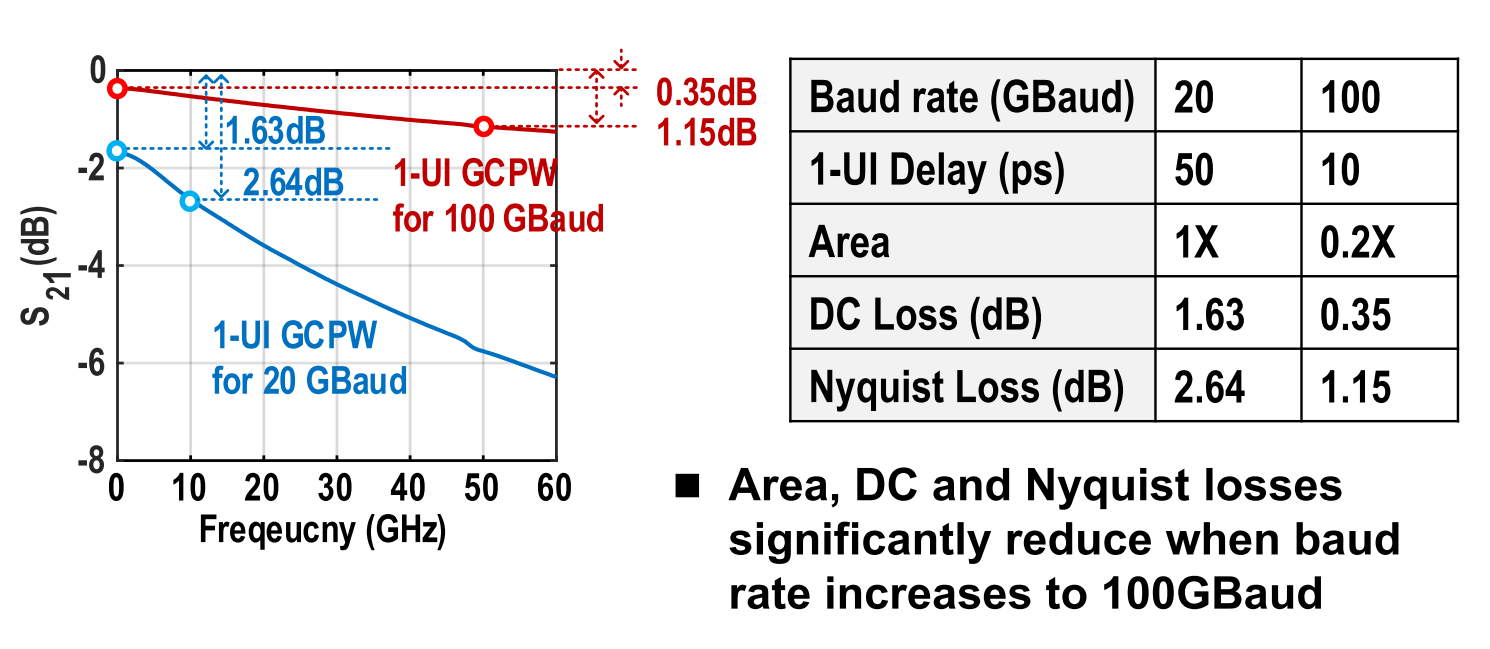

图1显示了两个片上接地共面波导(grounded coplanar waveguides, GCPW)的插入损耗,延迟分别为50ps和10ps,对应的单位间隔(UI)分别为20GBaud和100GBaud。50ps GCPW的长度约为7.5mm,在20GBaud FFE中使用时会导致显著的直流损耗和面积占用。为了避免长的片上传输线,一些设计利用集总电感器和电容器[5-6]作为无源延迟线。当波特率达到100GBaud时,单个UI GCPW的直流损耗和奈奎斯特损耗分别仅为0.35dB和1.15dB,远小于20GBaud的单个UI GCPW。这种损耗和面积的显著降低使得基于传输线的100GBaud FFE可行。

2. FFE Architecture

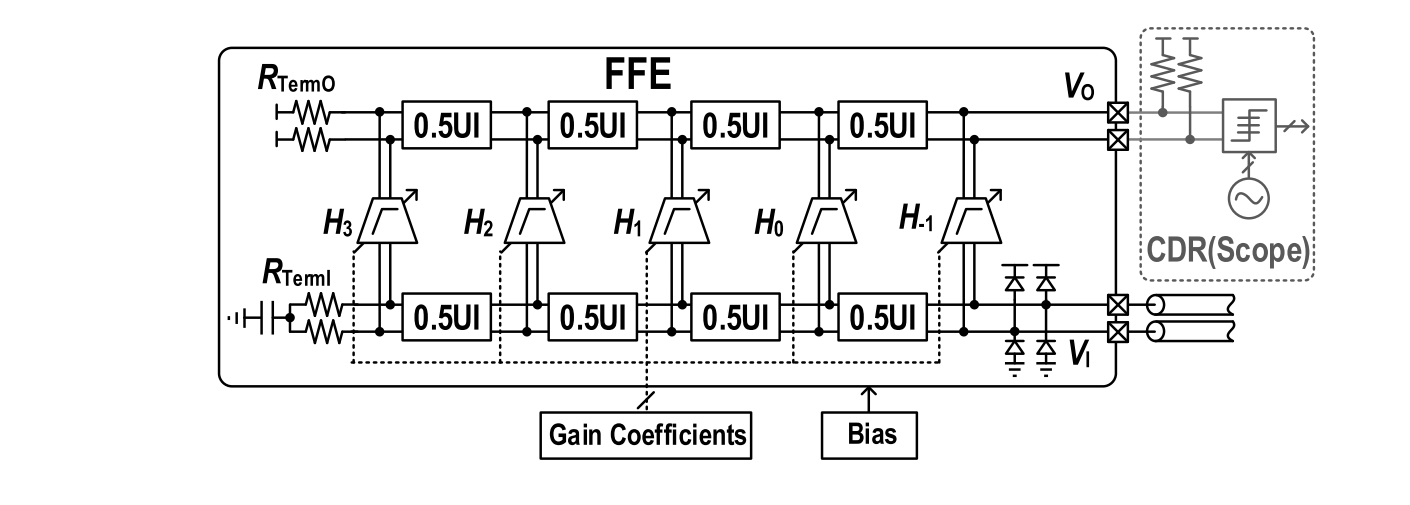

[^图2]: FFE Architecture

图2显示了本文中提出的的RX FFE的框图。输入数据VI通过2-UI延迟线并由AC接地电阻器RTermI终止。五个抽头H-1至H3以0.5 UI的间隔接收输入信号,并使用可编程增益系数将其放大。使用另一个0.5 UI间隔的延迟线对放大的信号求和,以生成FFE输出VO。该FFE支持传统的基于系数的中高频均衡,以及基于RC源退化的低频均衡。为了表征FFE的性能,使用了片外示波器来测量VO。

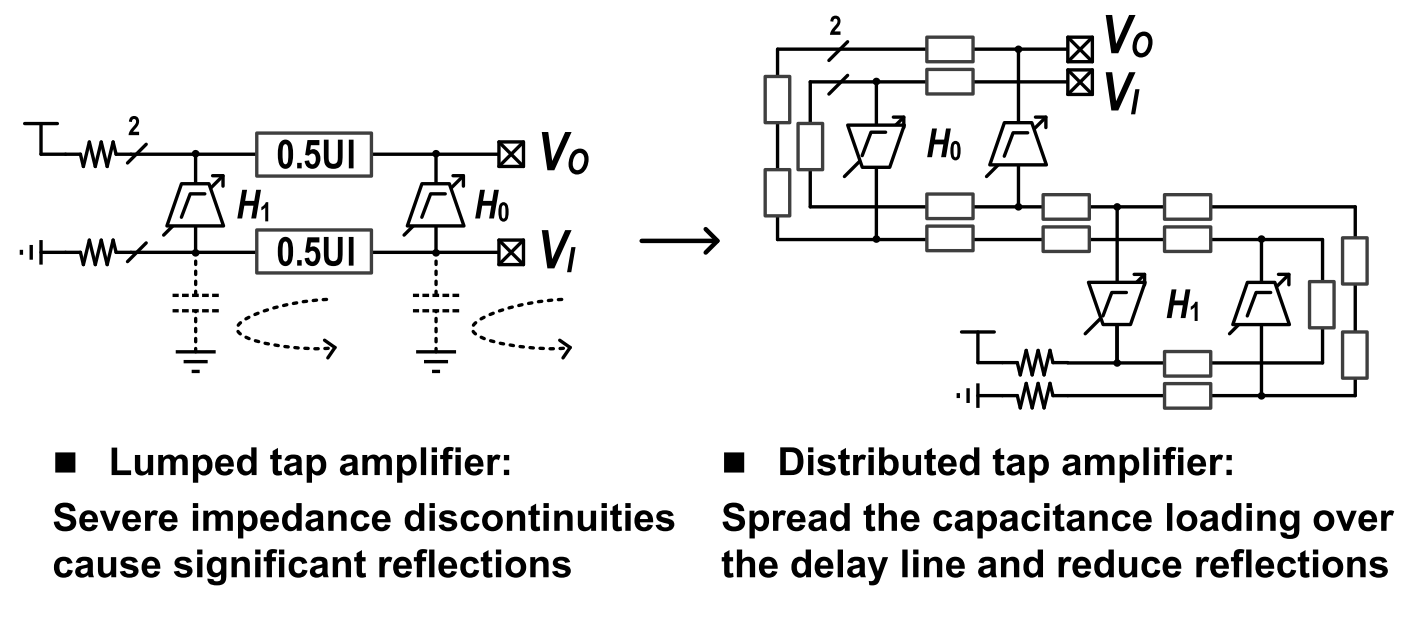

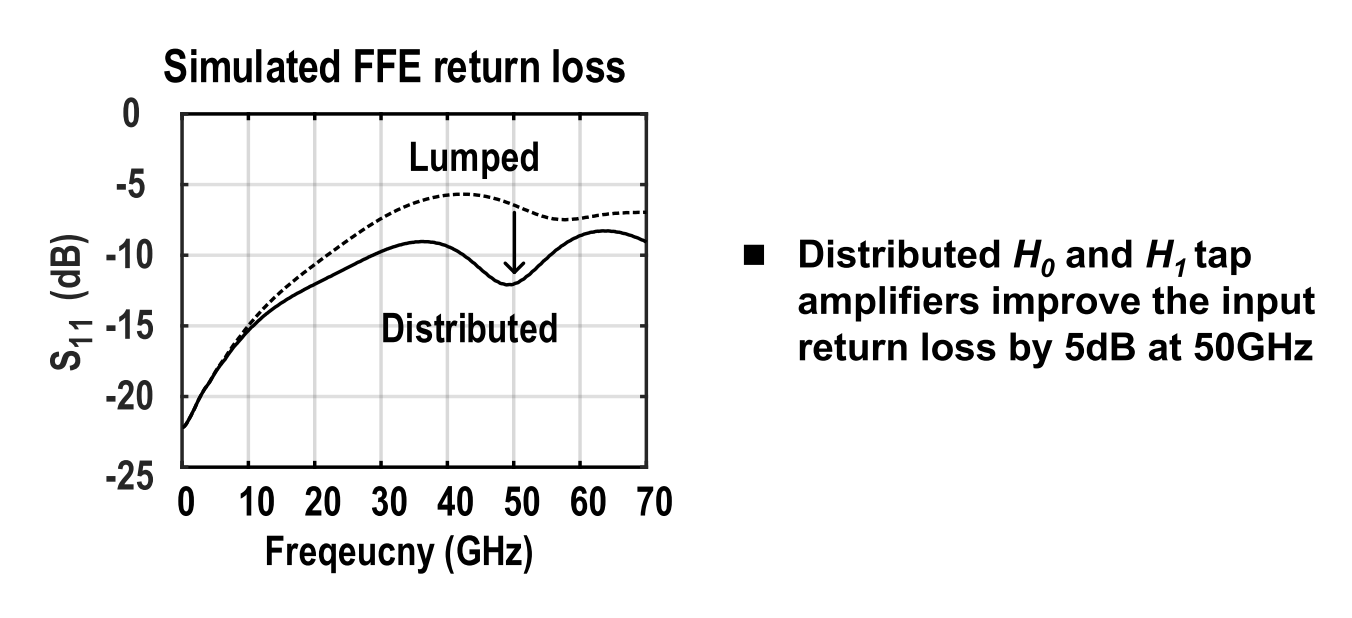

FFE采用单级拓扑结构,以实现更高的带宽和更低的功耗。由于在28nm CMOS工艺中实现带宽大于50GHz的放大器比较困难,因此本设计既没有实现输入缓冲器,也没有实现输出驱动器。因此,H0和H1抽头中的大型集总放大器(占总容性负载的2/3)会导致阻抗不连续,并引起明显的反射,如图3左边所示。其他三个抽头H-1、H2和H3相对较小,采用集总放大器实现。

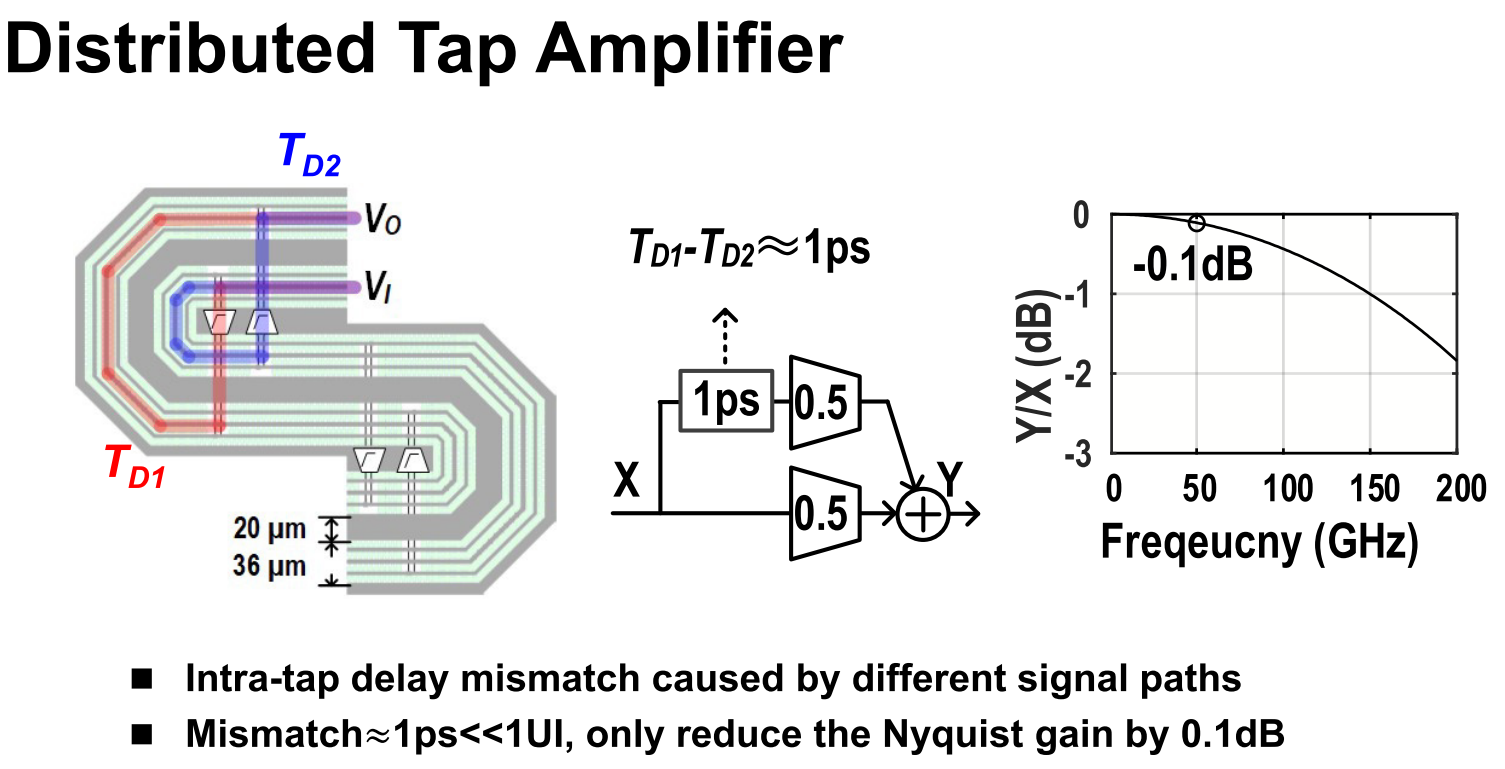

反射问题可以通过在H0和H1抽头中使用分布式放大器来缓解,如图4所示。虽然有1ps的抽头内延迟失配,但它只降低了0.1dB的奈奎斯特增益。

图5的仿真结果表明,H0和H1抽头放大器的分布使FFE在奈奎斯特频率下的回波损耗提高了5dB。

延迟线的阻抗被设计为60Ω而不是50Ω,以补偿抽头放大器的电容性负载引起的阻抗下降。

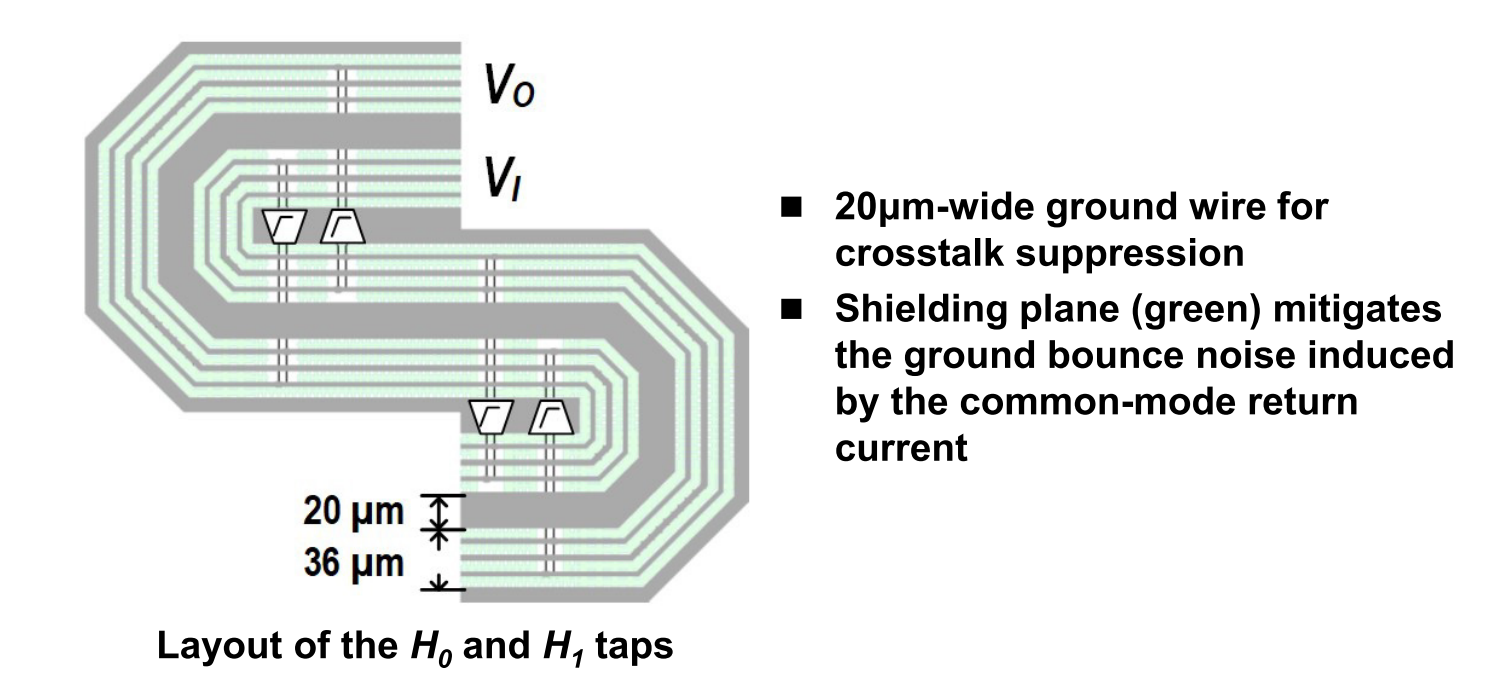

采用GCPW实现了输入VI和输出VO的两条延迟线,并在两条延迟线之间插入了20μm宽的地线以抑制串扰。高速延迟线下方的绿色屏蔽层提供低电阻接地,这显著地减轻了由抽头放大器的共模返回电流引起的地反弹噪声。

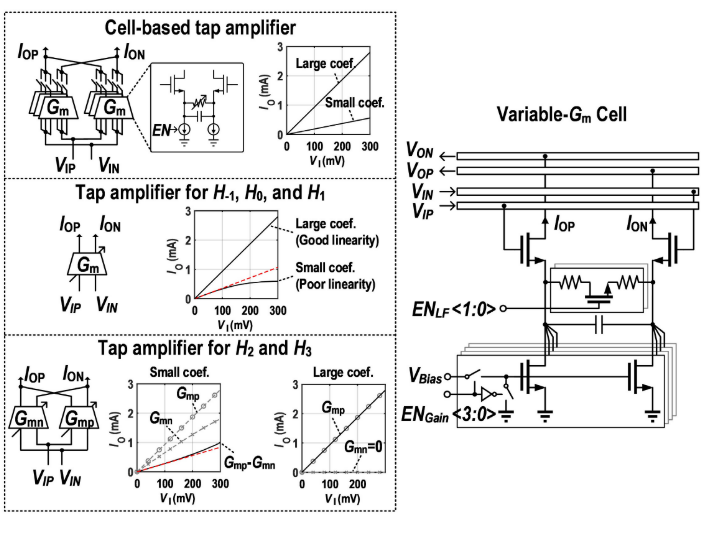

图8的左边显示了三种类型的抽头放大器。左上角是传统的基于单元的抽头放大器[5]。因为每个跨导(Gm)单元在相同的优化尾电流下操作,所以用任何系数都可实现良好的线性。然而,由多个Gm单元组成的抽头放大器遭受大的布线寄生效应,因为每个Gm单元必须独立地支持RC退化。H-1、H0和H1的抽头放大器利用尾电流控制可变跨导单元来实现更小的布线寄生效应,如左中所示。这三个抽头的系数远大于零,可防止近阈值电压工作引起严重的非线性。H2或H3的抽头放大器由两个输出交叉连接的可变跨导单元组成,如左下角所示。两个单元格的Gm相减使能小系数。仅使用一个Gm单元来实现大系数,而关闭另一个。结果,抽头放大器对于所有系数保持良好的线性。图6.3.3的右边是可变跨导电池的示意图。其增益由分辨率为4位的尾电流控制。2b可编程电阻的RC源极负反馈提供低频均衡。与增加更多FFE抽头相比,源极退化不消耗额外功率。此外,差分对的线性度得到改善,这有利于PAM4信令。H0和H1抽头分别由四个和两个可变Gm单元组成,以支持更大的系数和更精细的低频均衡调整。

Manufacturing parameters and test results(制造参数及测试结果)

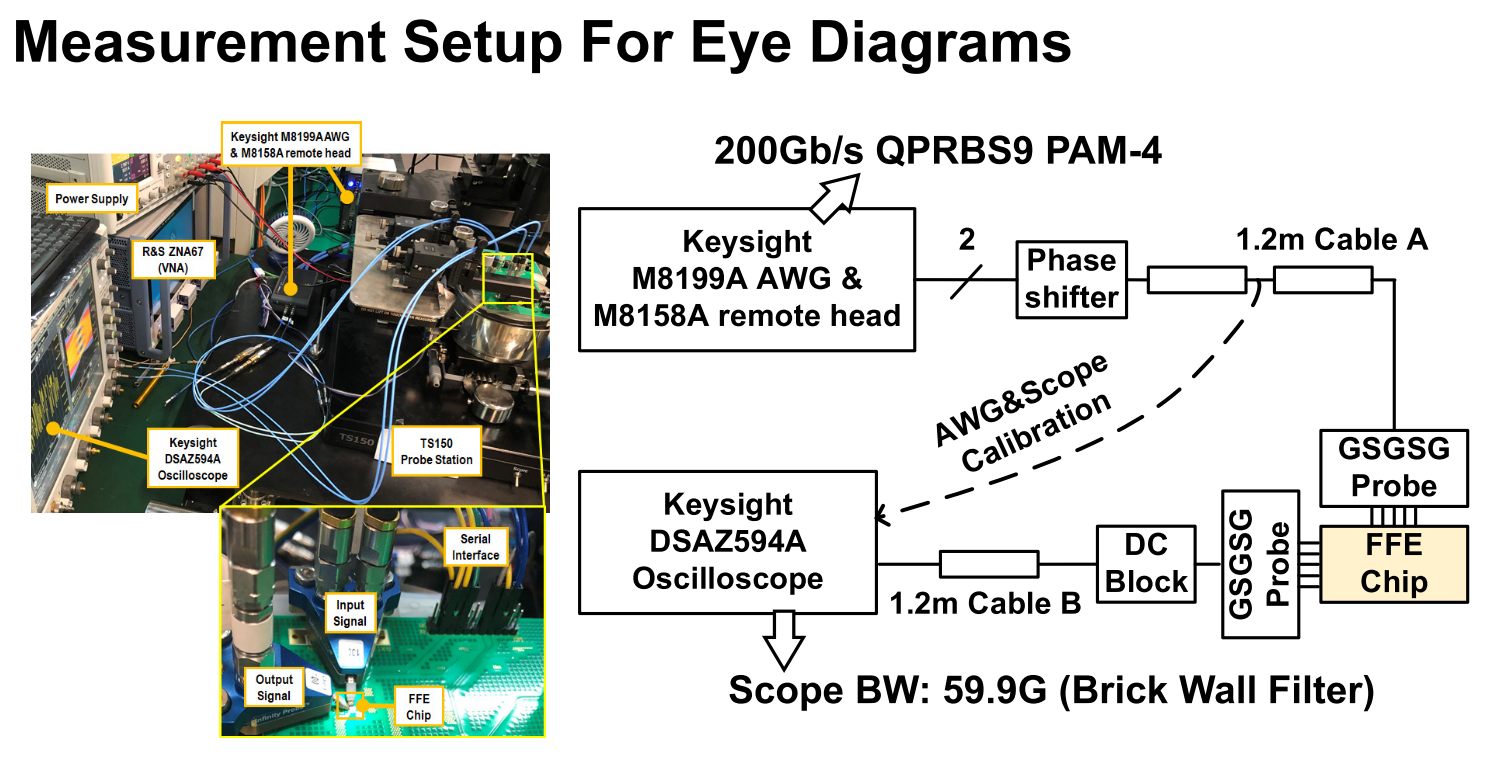

FFE采用28nm CMOS工艺制作。时域性能使用任意波形发生器(AWG)和实时示波器表征,频域性能使用矢量网络分析仪测量。

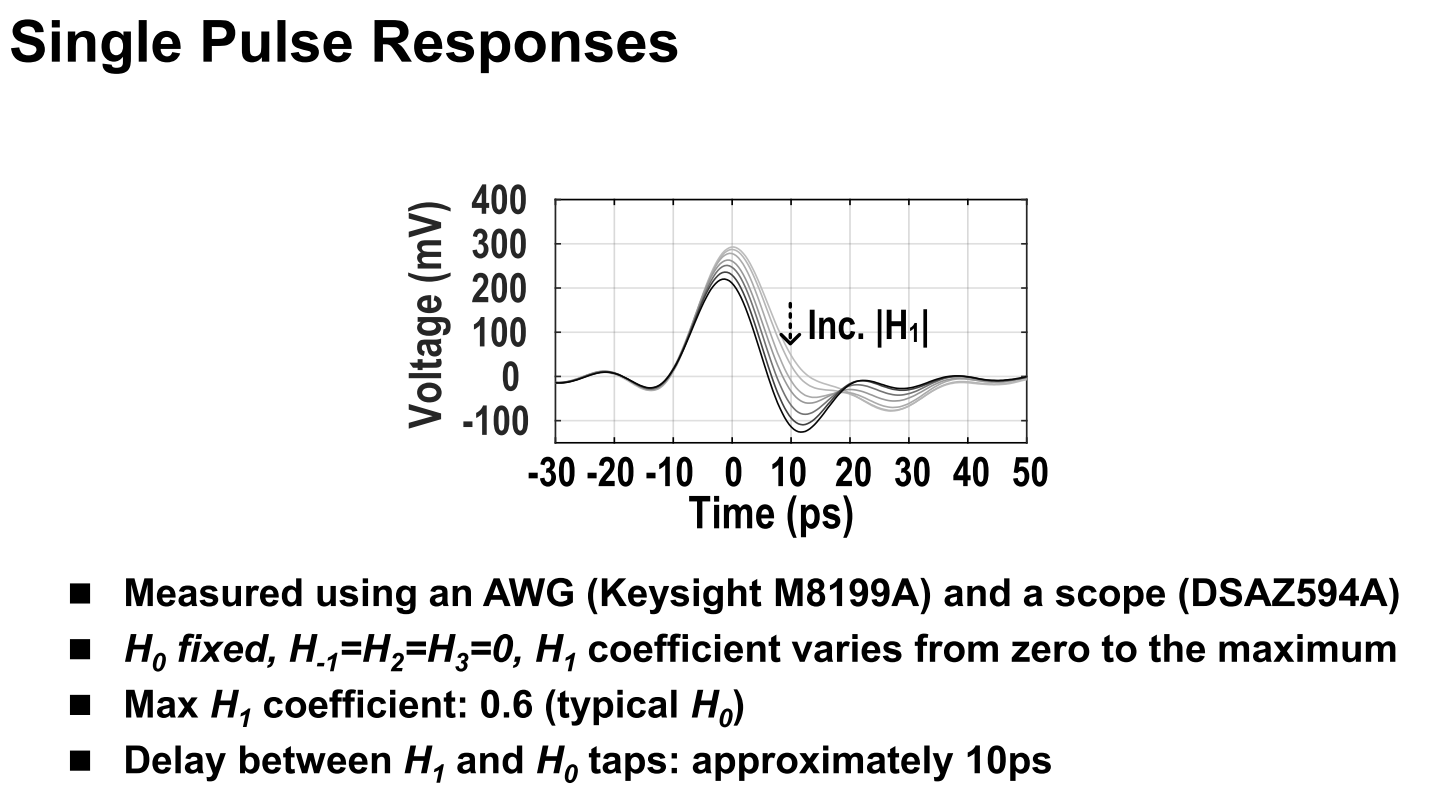

[^图9]: H0 + H1抽头的实测脉冲响应

图9显示了H0 + H1抽头的实测脉冲响应,H1系数从零变化到最大值,典型值为H0,其他抽头关闭。脉冲响应显示H1抽头具有0.6的最大归一化增益和大约10ps的延迟。

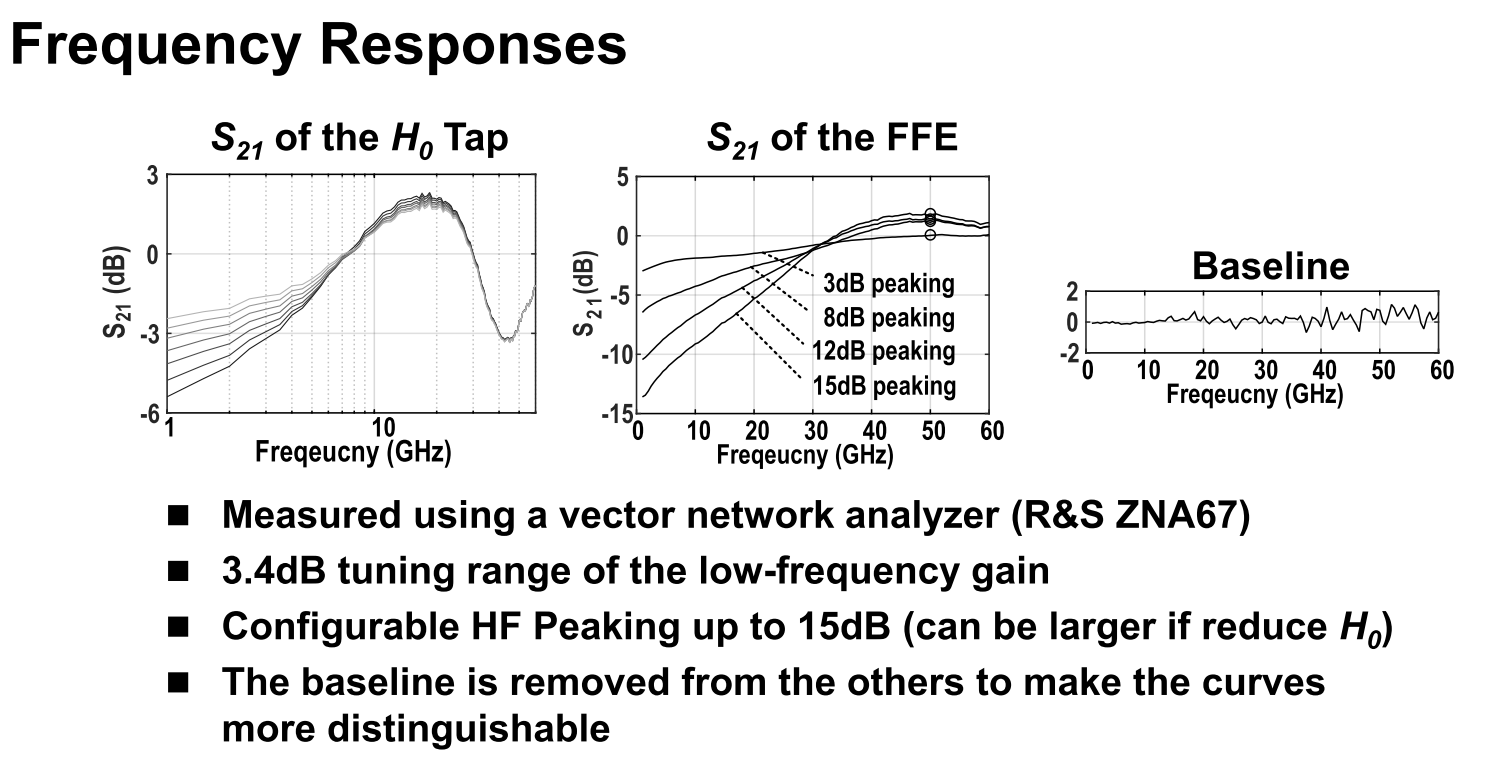

图10左边显示了H0抽头的频率响应,显示了低频增益的3.4dB调谐范围。5抽头FFE的频率响应可以配置为提供高达15dB的宽峰化范围,奈奎斯特增益为1.7dB,如图10中间所示。通过降低H0增益可以实现更大的峰化值。测量平坦的频率响应并将其用作基线,将其从其它频率响应中移除以使曲线更易区分。

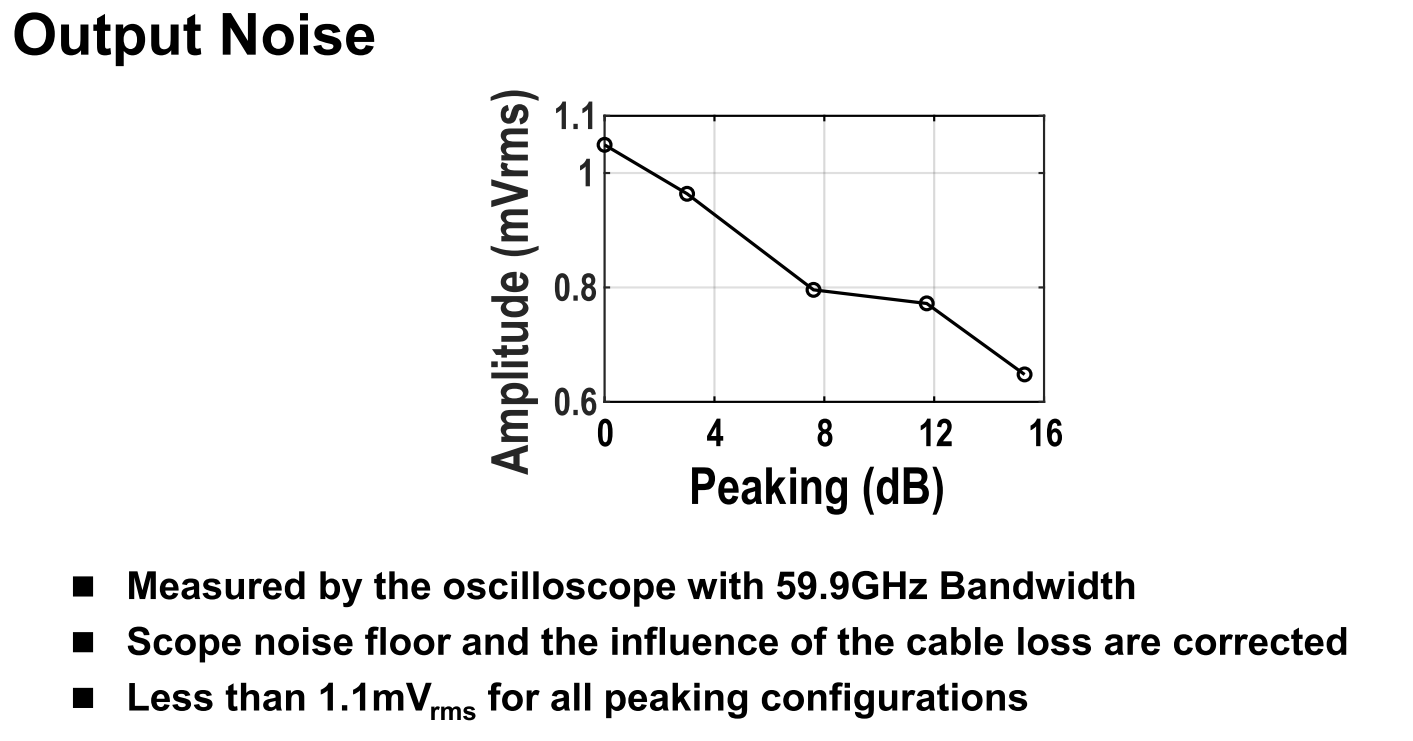

图11显示了FFE的实测输出噪声,所有峰化配置下的输出噪声均小于1.1mVrms。当在RX中实现时,由于其它电路引起的电源噪声,该数目将稍微增加。

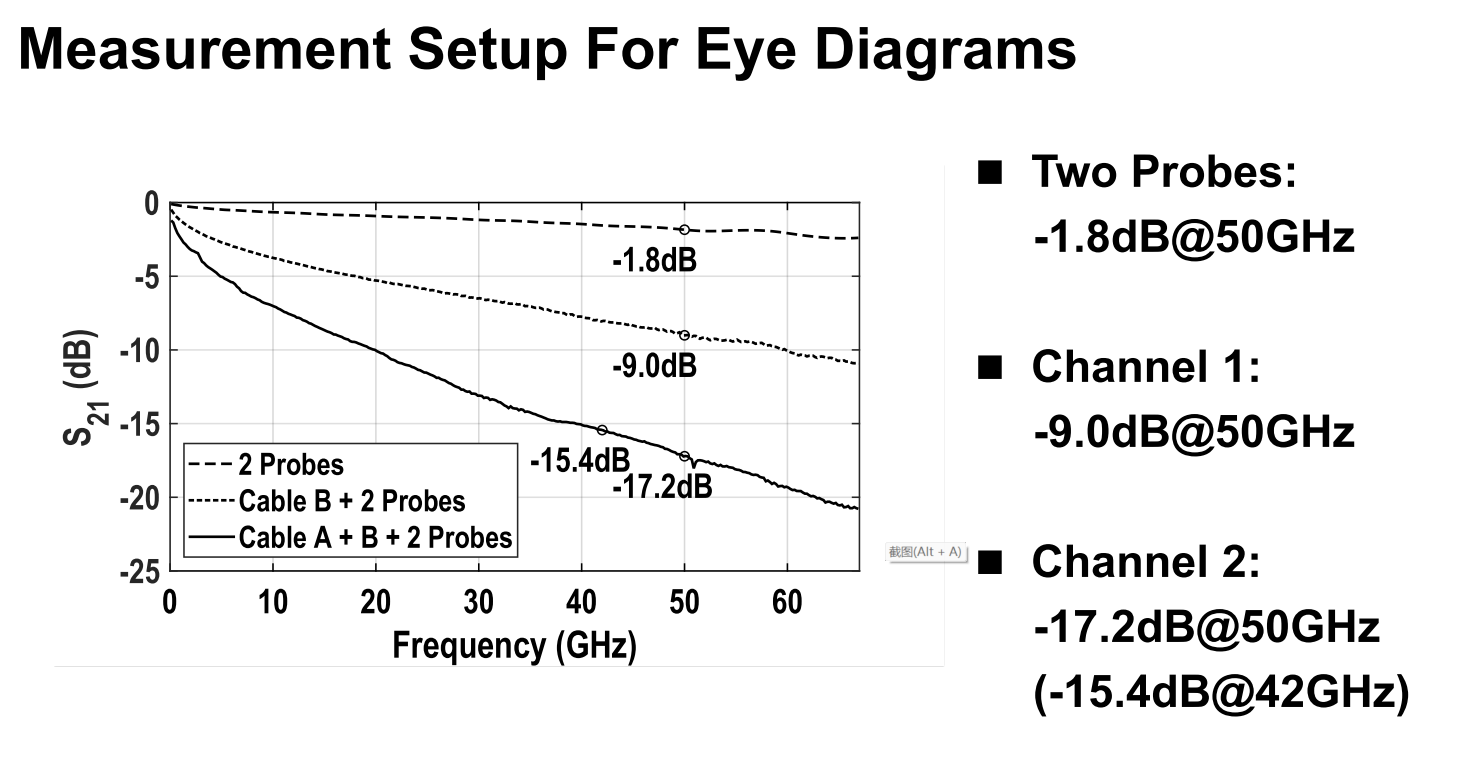

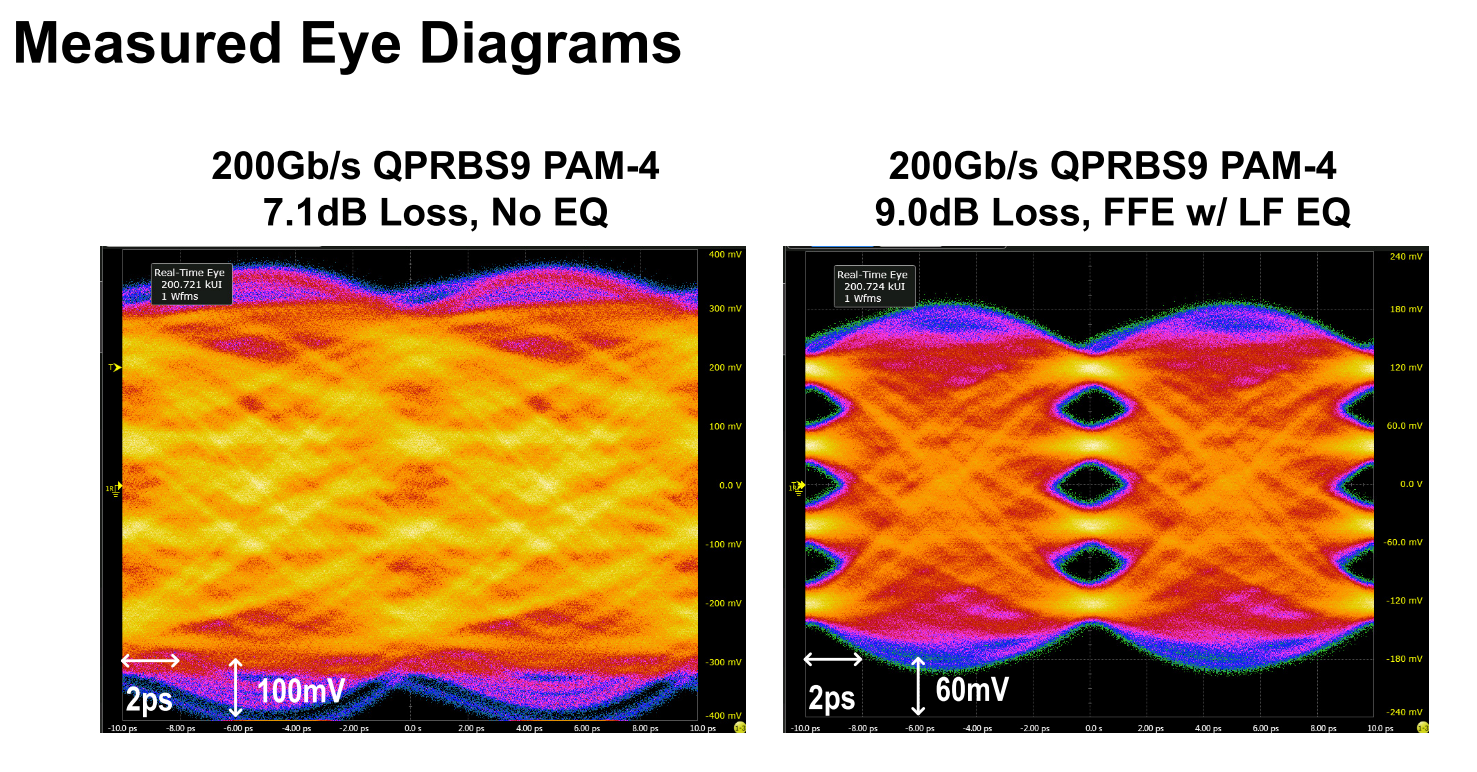

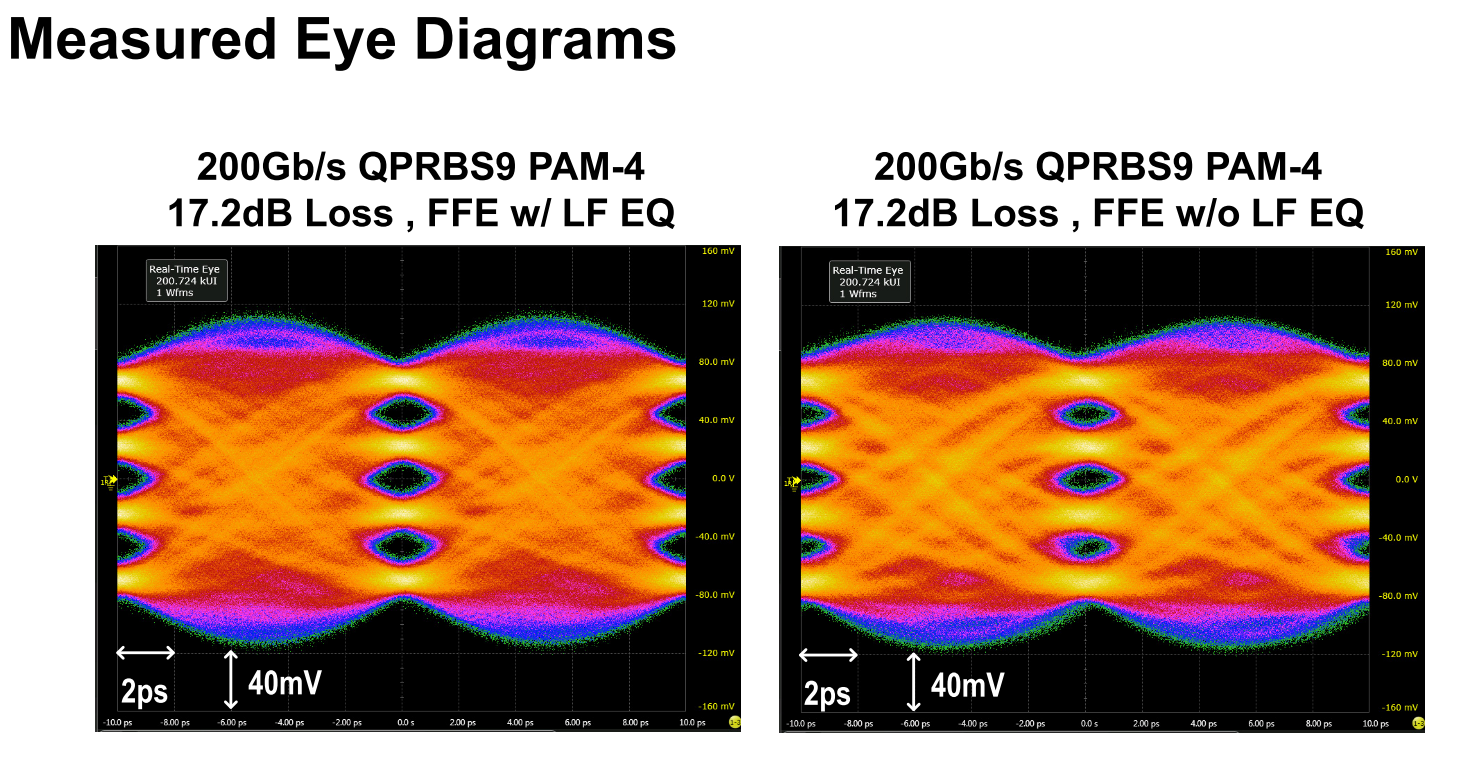

利用AWG产生200 Gb/s QPRBS 9 PAM-4信号,通过RX FFE,并由示波器捕获以测量眼图。测量了两个测试通道,包括射频探头和电缆,在50 GHz下的插入损耗分别为9.0dB和17.2dB。

图13显示了均衡前后的眼图。经过7. 1dB的电缆损耗后,眼图完全闭合。通过优化FFE系数和低频均衡,眼图在9.0dB和17.2dB损耗信道下都是开放的,在2 E5个符号上没有观察到错误。但是,示波器不支持PAM-4 CDR,在较长时间记录时会引起较大的低频抖动。在信道损耗为17. 2dB时,由眼图高度和噪声幅度计算得到的误码率小于1 E-6。当低频均衡关闭时,FFE系数很难恢复出17. 2dB损耗信道下的PAM-4信号。

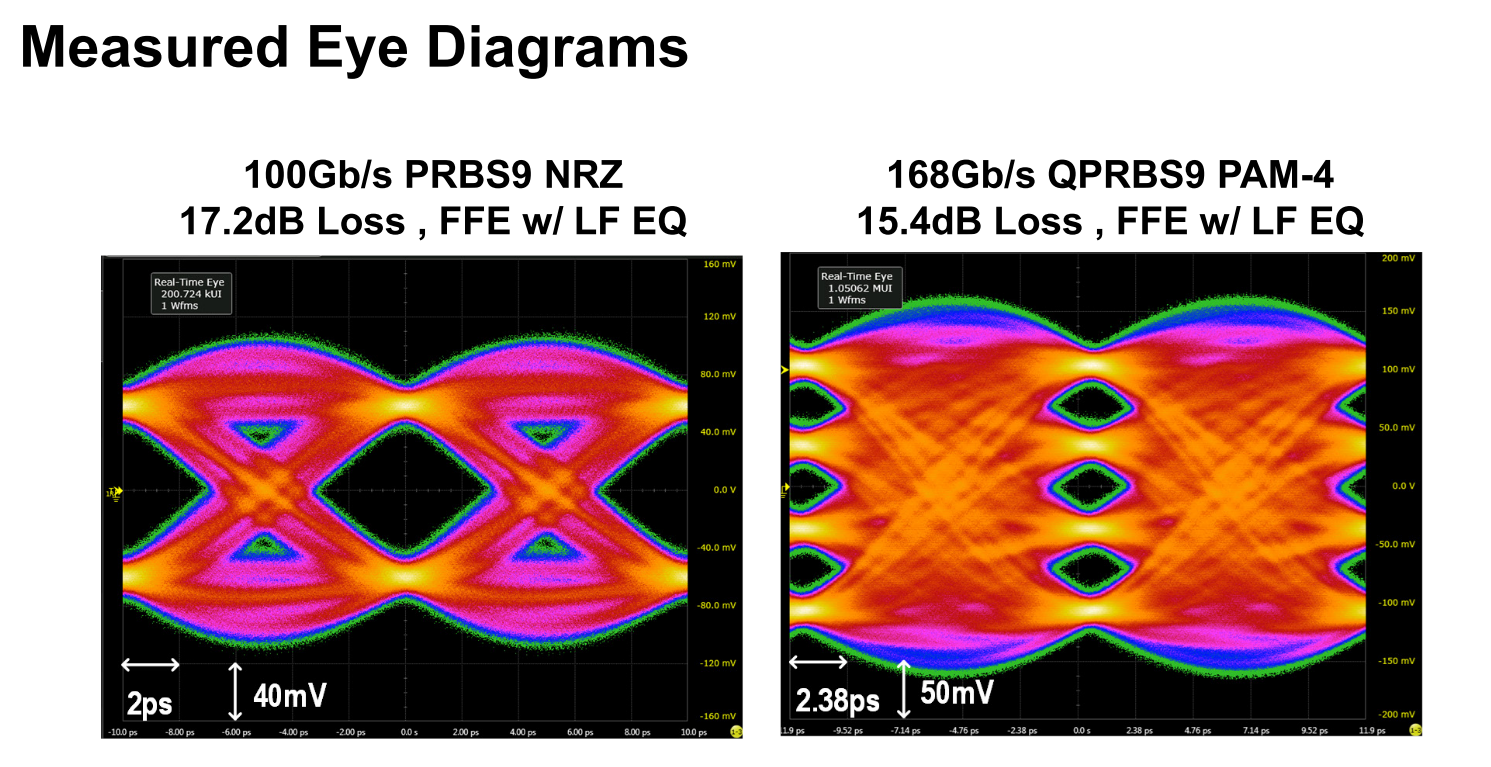

图14显示了同一通道的均衡100 Gb/s NRZ眼图。当工作在168 Gb/s的数据速率时,FFE在42 GHz处还补偿了15.4dB的损耗。对于17.2dB均衡,由2.2V电源供电,芯片的FFE功耗为115 mW,偏置和串行接口功耗为2 mW。当FFE在接收机中实现并从输出延迟线两端的50Ω电阻中抽取电流时,电源电压和总功耗分别可降低到1.6V和86mW。

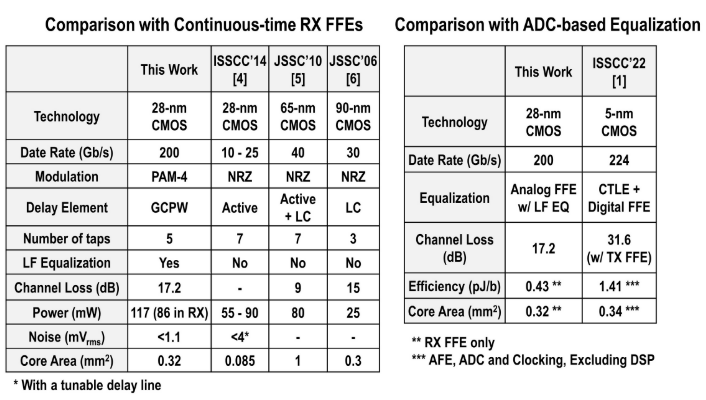

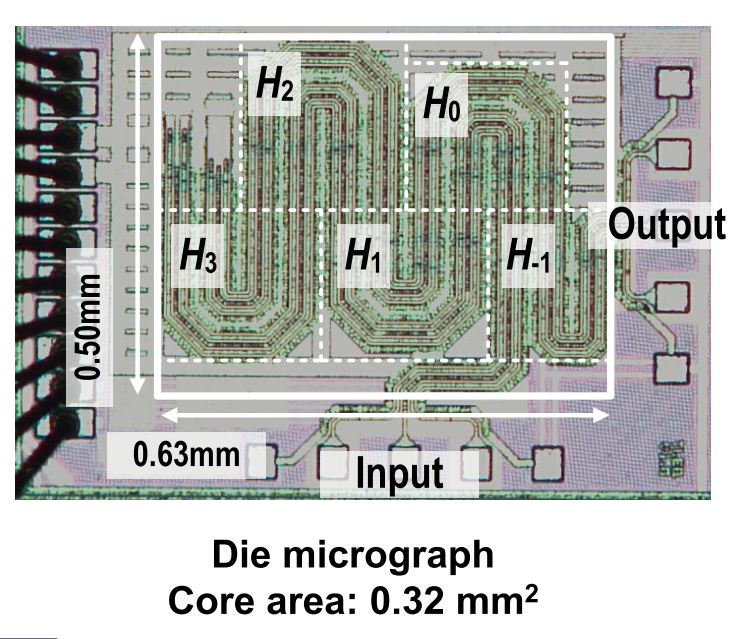

图15显示了测得的性能以及与之前发布的连续时间FFE和基于ADC的224 Gb/s RX [1]的比较。这是第一个工作在200 Gb/s的连续时间FFE。这里,低频均衡增强了信道损耗补偿。此外,无源延迟线和单级拓扑实现了低输出噪声。当在200 Gb/s接收机中实现时,所提出的FFE为短距离传输提供了一种低功耗的解决方案。0.43pJ/B的能效仅为基于ADC的RX的31%,0.32mm2的内核面积相当,尽管芯片中实现了无源传输线。

die的显微照片如图16所示。

更多论文分享关注[芯路探灿]公众号